從AI伺服器談HBM、HBM2、HBM3、HBM3e技術

HBM:突破視訊記憶體瓶頸,釋放AI伺服器效能

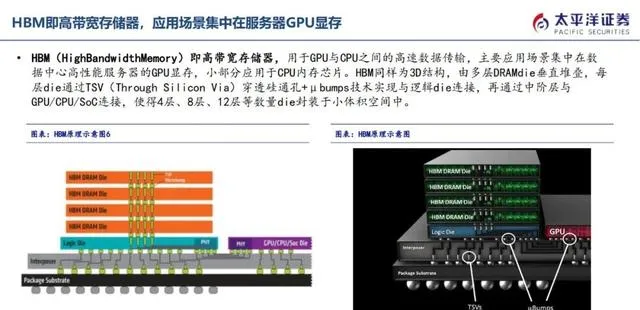

HBM(高頻寬儲存)是專為滿足AI伺服器GPU視訊記憶體需求而設計的創新儲存解決方案。它采用多層DRAM Die垂直堆疊技術,透過TSV穿透矽通孔技術實作與邏輯Die連線,使8層或12層Die封裝於小體積空間中,實作小尺寸、高頻寬、高傳輸速度的相容。

HBM的優勢在於:

* 頻寬更大:HBM的頻寬可達傳統視訊記憶體的數倍,滿足AI伺服器對數據吞吐量的巨大需求。

* 體積更小:HBM的體積僅為傳統視訊記憶體的幾分之一,有助於減小AI伺服器的整體尺寸。

* 功耗更低:HBM的功耗更低,可有效降低AI伺服器的執行成本。

HBM技術已經成為高效能AI伺服器GPU視訊記憶體的主流解決方案,為AI伺服器的效能提升提供了堅實的基礎。即高頻寬儲存,由多層DRAM Die垂直堆疊,每層Die透過TSV穿透矽通孔技術實作與邏輯Die連線,使得8層、12層Die封裝於小體積空間中,從而實作小尺寸於高頻寬、高傳輸速度的相容,成為高效能AI伺服器GPU視訊記憶體的主流解決方案。

HBM3E:更高速度、更大容量的記憶體解決方案

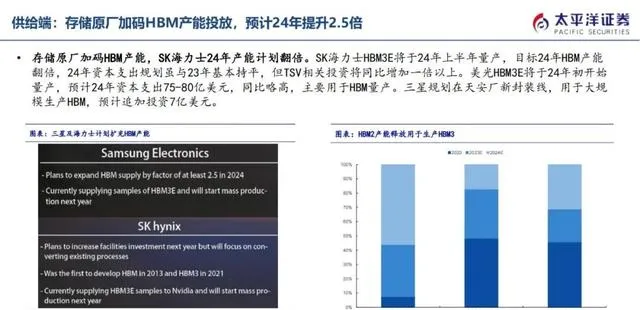

SK海力士率先釋出HBM3E,這是HBM3的擴充套件版本,提供高達8Gbps的傳輸速度和16GB記憶體。該記憶體解決方案將於2024年量產,將為下一代高效能計算、人工智能和圖形套用提供強大的支持。

HBM3E的特點

- 傳輸速度高達8Gbps,比HBM3提高了50%。

- 記憶體容量高達16GB,是HBM3的兩倍。

- 功耗更低,可滿足下一代高效能計算套用的需求。

HBM3E的套用

- 高效能計算:HBM3E將成為下一代高效能計算系統的關鍵元件,為科學研究、工程模擬等領域提供強大的計算能力。

- 人工智能:HBM3E也將成為人工智能套用的關鍵元件,為機器學習、深度學習等領域提供強大的數據處理能力。

- 圖形套用:HBM3E還將成為圖形套用的關鍵元件,為遊戲、虛擬現實等領域提供強大的圖形處理能力。HBM3的擴充套件版本HBM3E,提供高達8Gbps的傳輸速度和16GB記憶體,由SK海力士率先釋出,將於2024年量。

HBM:引領AI伺服器高速發展

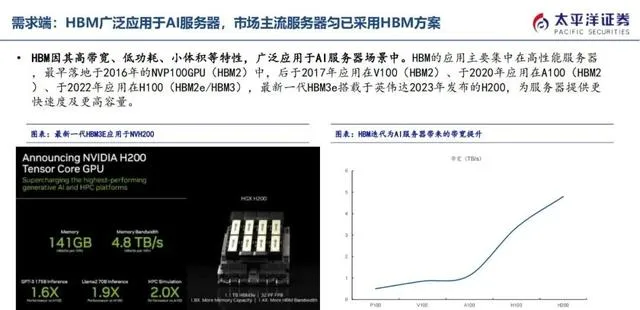

HBM(High Bandwidth Memory)以其超高頻寬和低功耗的優勢,成為AI伺服器的理想記憶體解決方案。最新一代HBM3e搭載於輝達2023年釋出的p00,為AI計算提供更強大的動力。

據Trendforce數據,2022年AI伺服器出貨量達到86萬台,預計2026年將超過200萬台,年復合增長率高達29%。隨著AI套用的不斷擴充套件,HBM市場也將迎來爆發式增長。

作為HBM領域的領導者,我們致力於提供高效能、低功耗的HBM解決方案,助力AI伺服器行業實作快速發展。主要套用場景為AI伺服器,最新一代HBM3e搭載於輝達2023年釋出的p00。根據Trendforce數據,2022年AI伺服器出貨量86萬台,預計2026年AI伺服器出貨量將超過200萬台,年復合增速29%。

AI伺服器HBM需求爆發,市場規模迅猛增長

● AI伺服器出貨量大幅增長,帶動HBM需求爆發。

● 伺服器平均HBM容量不斷增加,進一步推動市場需求。

● 預計2025年HBM市場規模將達150億美元,年復合增長率超過50%。伺服器出貨量增長催化HBM需求爆發,且伴隨伺服器平均HBM容量增加,經測算,預期25年市場規模約150億美元,增速超過50%。

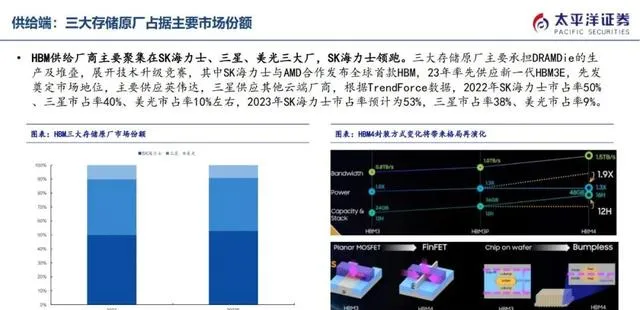

三強鼎立,SK海力士領跑HBM市場。2023年,SK海力士市占率預計達53%,三星緊隨其後,市占率為38%,而美光則為9%。

工藝演進,CoWoS和TSV引領風潮。HBM在工藝上不斷革新,以追求更高的頻寬和更低的功耗。CoWoS (Chip-on-Wafer-on-Substrate) 和 TSV (Through-Silicon Via) 等技術正在成為主流。

HBM,引領儲存技術新潮流。憑借其超高頻寬和低功耗的特性,HBM正在成為高效能計算、人工智能和數據中心等領域的理想選擇。供給廠商主要聚集在SK海力士、三星、美光三大儲存原廠,根據Trendforce數據,2023年SK海力士市占率預計為53%,三星市占率38%、美光市占率9%。HBM在工藝上的變化主要在CoWoS和TSV。

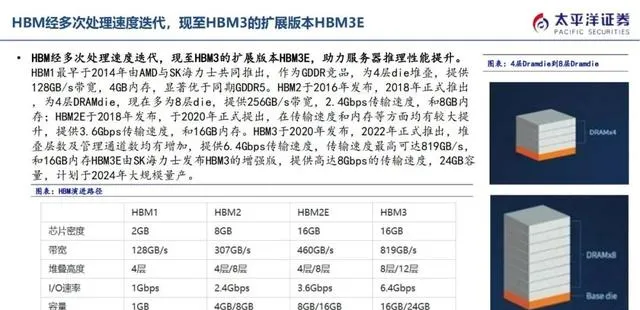

- 2014年,AMD與SK海力士聯手推出HBM1,挑戰GDDR視訊記憶體。

- HBM1采用4層die堆疊設計,提供128GB/s頻寬,遠超同時期GDDR5視訊記憶體。

- HBM1記憶體容量高達4GB,優於同期視訊記憶體。最早於2014年由AMD與SK海力士共同推出,作為GDDR競品,為4層die堆疊,提供128GB/s頻寬,4GB記憶體,顯著優於同期GDDR5。

HBM系列DRAM技術的發展歷程:

- HBM2:

- 釋出年份:2016年

- 正式推出:2018年

- DRAM die層數:4層

- 多層die:8層

- 頻寬:256GB/s

- 傳輸速度:2.4Gbps

- 記憶體:8GB

- HBM2E:

- 釋出年份:2018年

- 正式提出:2020年

- 傳輸速度:3.6Gbps

- 記憶體:16GB

- HBM3:

- 釋出年份:2020年

- 正式推出:2022年

- DRAM die層數:增加

- 管理通道數:增加

- 傳輸速度:6.4Gbps(最高可達819GB/s)

- 記憶體:16GB

- HBM3E:

- 釋出單位:SK海力士

- 釋出年份:待定,計劃於2024年大規模量產

- 傳輸速度:高達8Gbps

- 記憶體:24GB於2016年釋出,2018年正式推出,為4層DRAMdie,現在多為8層die,提供256GB/s頻寬,2.4Gbps傳輸速度,和8GB記憶體;HBM2E於2018年釋出,於2020年正式提出,在傳輸速度和記憶體等方面均有較大提升,提供3.6Gbps傳輸速度,和16GB記憶體。HBM3於2020年釋出,2022年正式推出,堆疊層數及管理通道數均有增加,提供6.4Gbps傳輸速度,傳輸速度最高可達819GB/s,和16GB記憶體HBM3E由SK海力士釋出HBM3的增強版,提供高達8Gbps的傳輸速度,24GB容量,計劃於2024年大規模量產。

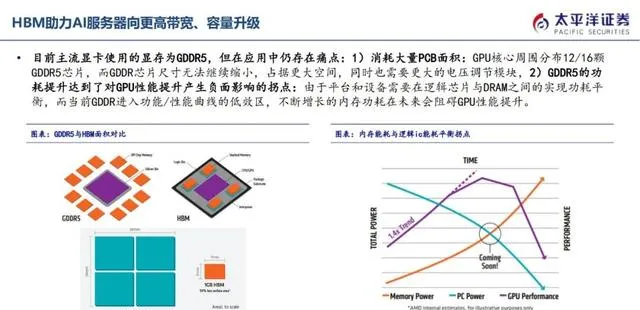

HBM,全稱為高頻寬記憶體,具備傳輸速度快、功耗低、體積小巧等優勢,是AI伺服器場景的理想儲存解決方案。

自2016年首次套用於NVIDIA的NVP100 GPU(HBM2)以來,HBM得到了業界的廣泛認可,相繼被采用於V100(HBM2)、A100(HBM2)、p00(HBM2e/HBM3)等系列GPU中。

最新一代的HBM3e記憶體搭載於輝達2023年釋出的p00 GPU上,進一步提升了速度和容量,為伺服器提供了更強大的效能支持。HBM的出現標誌著伺服器記憶體技術的發展邁入了一個新時代,其高頻寬、低功耗、小體積等特性,為人工智能、深度學習等領域的高效能計算提供了強有力的支撐,並有望在未來發揮更加重要的作用。因其高頻寬、低功耗、小體積等特性,廣泛套用於AI伺服器場景中。HBM的套用主要集中在高效能伺服器,最早落地於2016年的NVP100GPU(HBM2)中,後於2017年套用在V100(HBM2)、於2020年套用在A100(HBM2)、於2022年套用在p00(HBM2e/HBM3),最新一代HBM3e搭載於輝達2023年釋出的p00,為伺服器提供更快速度及更高容量。

HBM市場概況:

- SK海力士、三星、美光三巨頭主導HBM市場,SK海力士領跑;

- 三大廠商專註於DRAM Die生產和堆疊,技術升級競賽激烈。

SK海力士優勢明顯:

- 與AMD合作釋出全球首款HBM,率先供應新一代HBM3E,奠定市場地位;

- 主要供應輝達,市占率領先,預計2023年將進一步提升至53%。

三星緊隨其後:

- 主要供應其他雲端廠商,市占率預計2023年將降至38%;

- 技術實力強勁,與SK海力士展開激烈競爭。

美光穩居第三:

- 市占率預計2023年將降至9%;

- 專註於高端HBM市場,技術研發實力不容小覷。

市場前景:

- HBM市場仍有較大增長潛力,預計未來幾年將保持穩定增長;

- 人工智能、5G等新興技術的發展將對HBM需求產生積極影響。供給廠商主要聚集在SK海力士、三星、美光三大廠,SK海力士領跑。三大儲存原廠主要承擔DRAMDie的生產及堆疊,展開技術升級競賽,其中SK海力士與AMD合作釋出全球首款HBM,23年率先供應新一代HBM3E,先發奠定市場地位,主要供應輝達,三星供應其他雲端廠商,根據TrendForce數據,2022年SK海力士市占率50%、三星市占率40%、美光市占率10%左右,2023年SK海力士市占率預計為53%,三星市占率38%、美光市占率9%。

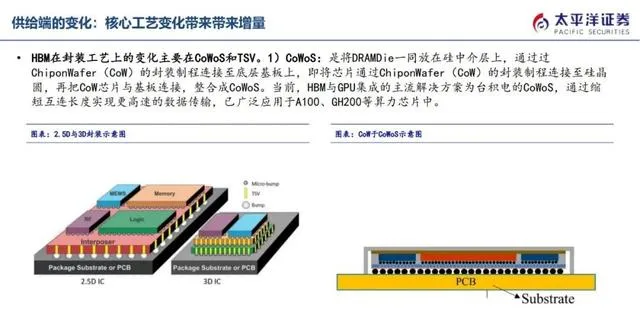

HBM在封裝工藝上的變化主要在CoWoS和TSV。

CoWoS,提升數據傳輸速度,整合GPU的理想解決方案

- CoWoS,將DRAM Die整合於矽中介層上,實作更快速的數據傳輸。

- 基於ChiponWafer(CoW)封裝技術,縮短互連長度,大幅提升數據傳輸速度。

- 廣泛套用於A100、Gp00等高效能計算芯片中。

- 台積電的高效CoWoS解決方案,滿足GPU整合需求,帶來更大頻寬和更高的效能。)CoWoS:是將DRAMDie一同放在矽中介層上,透過過ChiponWafer(CoW)的封裝制程連線至底層基板上,即將芯片透過ChiponWafer(CoW)的封裝制程連線至矽晶圓,再把CoW芯片與基板連線,整合成CoWoS。當前,HBM與GPU整合的主流解決方案為台積電的CoWoS,透過縮短互連長度實作更高速的數據傳輸,已廣泛套用於A100、Gp00等算力芯片中。

TSV矽通孔是實作HBM容量和頻寬擴充套件的核心技術,在整個矽晶圓厚度上打孔,形成數千個垂直互連,連線芯片正面和背面。HBM中,多層DRAM die堆疊,透過TSV和焊接凸點連線,只有最底部的die能外部連線到儲存控制器,其余管芯則透過內部TSV互連。TSV技術顯著提升了HBM的效能和密度,使其成為高效能計算和人工智能領域的理想選擇。)TSV:TSV矽通孔是實作容量和頻寬擴充套件的核心,透過在整個矽晶圓厚度上打孔,在芯片正面和背面之間形成數千個垂直互連。在HBM中多層DRAMdie堆疊,透過矽通孔和焊接凸點連線,且只有最底部的die能向外連線到儲存控制器,其余管芯則透過內部TSV實作互連。

-對此,您有什麽看法見解?-

-歡迎在評論區留言探討和分享。-