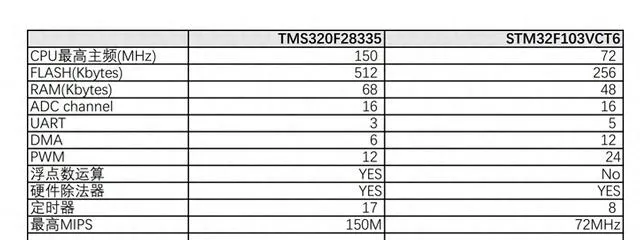

对于在高频静电除尘电源控制器中,用STM32F103VCT6处理器替代TI的DSP TMS320F28335核心板的可行性,我是这样考虑的:

CPU计算能力

28335的CPU运行主频为150MHz,一秒钟可以执行150MHz的单时间周期指令,

有高效的硬件浮点数运算单元,64位整数除以32位整数运算耗时1条指令周期;

32位整数乘以32位整数运算耗时1条指令周期;

如果STM32F103处理器的主频为72MHz,

32位整数乘以32位整数运算耗时2条指令周期;

64位整数除以32位整数运算最长耗时为8条指令周期,

32位整数加、减运算耗时为1条指令周期;

因为之前设计代码时就考虑到浮点数运算比较耗时,没有硬件浮点数运算单元时,单次的浮点数乘除法操作可能就耗时几十us,

所以,特意把代码中需要用到的浮点数运算转换为整数运算,乘以大于1的数,转为*65535除以小于65535的数,乘以小于1的数,转为乘以小于65535的数再除以65535;

从而把浮点数运算转为32位整数乘除法运算,

比如*0.35=22937/65535; *2.5=65535/26241等等;

资源对比

CPU负荷率

控制器代码中实时性要求高的任务主要包括:

周期为156.25us的14路ADC DMA完成中断,在该中断程序中,将ADC转换数值加入到累加和中,如果ADC采样累计次数达到了128次,即对应20ms,则对累加和除以次数,得到ADC的平均值,并在主循环中对平均值进行标定,得到测量值,与此同时,还根据单次采样数值进行电场的闪络判断以及保护;

预计在累计次数达到128次,中断程序需要执行大约1000条指令,耗时约1000/72MHz=13us;

RS485通信的串口接收中断以及发送,当前的程序是每接收或者发送一个字节就运行中断程序,进行发送数据的准备以及接收数据缓存以及RS485的收发时间间隔的判断,

两个RS485通信的串口中断总执行了大约100条指令,耗时约1.25us,而如果采用19200bps的波特性,一个字节的时间间隔即串口中断程序执行的周期为520us;

systick中断,用于产生系统时基,在systick中断时间间隔为500us,在中断程序中主要是定时标志位置位,以及MODBUS通信字节间隔的判断,用于完成接收以及启动发送。

执行了大约300条指令,耗时约4us;

实测如下:

ADC中断运行时间:22us;

systick中断运时间:5us;

MODBUS串口中断运行时间:2us;

因为,所有中断都是同一优先级,在所有中断同时发生的最坏情况下,总的中断运行时间为29us;

最短任务的周期为156.25us;

CPU的负荷率为18%;

远远小于负荷率小于30%的要求;

对于实时性要求最高的电场闪络检测及其输出关断保护,最坏情况下可能会有29us的延时,并不会导致检测以及关断不及时;

采用STM32F103处理器设计的核心板

其它资源的考虑

一路UART用于连接CAT1模块,用于将设备通过4G网络连接到云服务器,实现控制器的远程状态查看、操作和固件升级;

两路UART实现MODBUS从模式,其中一路MODBUS从模式用于连接工控屏,另一种用于数据远传;

DMA1的Channel1用于自动保存14路ADC的转换数值;

DMA1的Channel5用于自动接收来自于CAT1模块的串口数据,Chanel4用于自动发送数据到CAT1模块;

定时器TIM1以及TIM2用于产生IGBT的驱动波形,使用TIM1的PWM通道1以及TIM2的PWM通道2输出频率、占空比以及死区时间均可以调节的IGBT驱动波形;

定时器TIM8的若干个PWM通路用于输出母线电压、电流,二次电压、电流,滤成直流驱动电压、电流表显示数值。

定时器TIM4用于触发ADC启动组采样,溢出周期设置为156.25us,一个市电周期20ms可以采样128个数据;

由于STM32F103处理器内置的FLASH在进行擦除操作时,CPU会被挂起,使得闪络判断,IGBT驱动波形输出等的中断,会导致严重的问题,因为使用外置的spi flash芯片用于存储设置参数;

ADC初始化函数

ROM和RAM的使用情况如下:

Total RO Size (Code + RO Data) 35868 ( 35.03kB)

Total RW Size (RW Data + ZI Data) 19000 ( 18.55kB)

Total ROM Size (Code + RO Data + RW Data) 36156 ( 35.31kB)

用于4G远程通信的串口通信代码使用了比较大的RAM空间,接收和发送的DMA缓存各自占用了4KByte的RAM空间;