(報告出品方/作者:中國平安,付強、徐勇、徐碧雲)

周期復盤:封測底部上揚,先進封裝占比逐年走高

周期復盤∣半導體周期底部已築,開啟新一輪上升通道

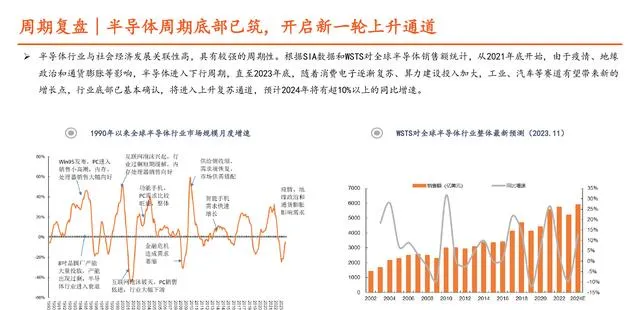

半導體行業與社會經濟發展關聯性高,具有較強的周期性。根據SIA數據和WSTS對全球半導體銷售額統計,從2021年底開始,由於疫情、地緣 政治和通貨膨脹等影響,半導體進入下行周期,直至2023年底,隨著消費電子逐漸復蘇、算力建設投入加大,工業、汽車等賽道有望帶來新的 增長點,行業底部已基本確認,將進入上升復蘇通道,預計2024年將有超10%以上的同比增速。

周期監控∣封測板塊可作為監測半導體周期內容的重要指標

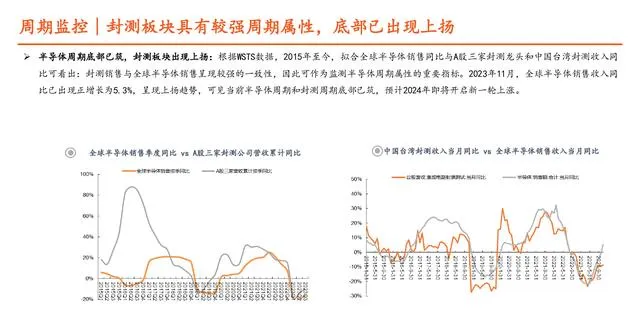

半導體封測環節是監測半導體周期內容的重要關口:封測產業處在半導體產業鏈的下遊,主要作用為對半導體芯片進行封裝、測試與檢測,屬 於資本密集型和人工密集型,直接對接下遊終端,因此下遊套用和需求變化將直接影響封測行業的技術路線和稼動率,二者之間存在強大的聯 動作用與配合機制。因此,與前道晶圓端一樣,後道封測產業也是監測半導體周期的重要指標。

周期監控∣封測板塊具有較強周期內容,底部已出現上揚

半導體周期底部已築,封測板塊出現上揚:根據WSTS數據,2015年至今,擬合全球半導體銷售同比與A股三家封測龍頭和中國台灣封測收入同 比可看出:封測銷售與全球半導體銷售呈現較強的一致性,因此可作為監測半導體周期內容的重要指標。2023年11月,全球半導體銷售收入同 比已出現正增長為5.3%,呈現上揚趨勢,可見當前半導體周期和封測周期底部已築,預計2024年即將開啟新一輪上漲。

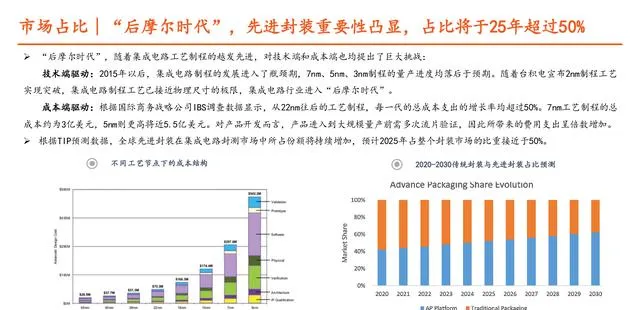

市場占比∣「後莫耳時代」,先進封裝重要性凸顯,占比將於25年超過50%

「後莫耳時代」,隨著積體電路工藝制程的越發先進,對技術端和成本端也均提出了巨大挑戰: 技術端驅動:2015年以後,積體電路制程的發展進入了瓶頸期,7nm、5nm、3nm制程的量產進度均落後於預期。隨著台積電宣布2nm制程工藝 實作突破,積體電路制程工藝已接近物理尺寸的極限,積體電路行業進入「後莫耳時代」。 成本端驅動:根據國際商務戰略公司IBS調查數據顯示,從22nm往後的工藝制程,每一代的總成本支出的增長率均超過50%。7nm工藝制程的總 成本約為3億美元,5nm則更高將近5.5億美元。對產品開發而言,產品進入到大規模量產前需多次流片驗證,因此所帶來的費用支出呈倍數增加。 根據TIP預測數據,全球先進封裝在積體電路封測市場中所占份額將持續增加,預計2025年占整個封裝市場的比重接近於50%。

競爭格局:台積電等龍頭領先,國內廠商產業鏈完善

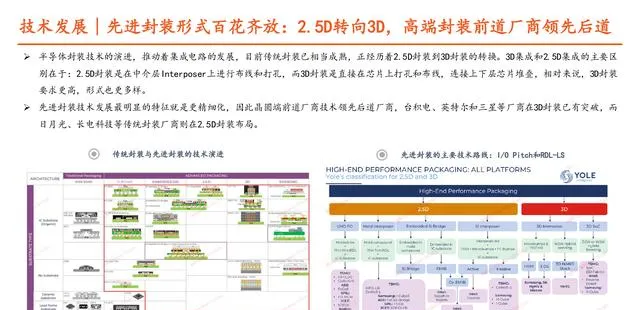

技術發展∣先進封裝形式百花齊放:2.5D轉向3D,高端封裝前道廠商領先後道

半導體封裝技術的演進,推動著積體電路的發展,目前傳統封裝已相當成熟,正經歷著2.5D封裝到3D封裝的轉換。3D整合和2.5D整合的主要區 別在於:2.5D封裝是在中介層Interposer上進行布線和打孔,而3D封裝是直接在芯片上打孔和布線,連線上下層芯片堆疊,相對來說,3D封裝 要求更高,形式也更多樣。 先進封裝技術發展最明顯的特征就是更精細化,因此晶圓端前道廠商技術領先後道廠商,台積電、英特爾和三星等廠商在3D封裝已有突破,而 日月光、長電科技等傳統封裝廠商則在2.5D封裝布局。

技術發展∣細化到關鍵技術節點,TSV/BUMP/RDL等更精細化

進一步細分到先進封裝的關鍵技術節點,不同的封裝形式有不同的判斷標準。一般來說區別各家封裝廠3D封裝技術能力的好差標準之一是TSV Diameter、I/O Pitch、RDL-LS的精度等。 根據Yole統計,目前一般先進封裝Bump I/O Pitch大約在50um左右,3D Stack Pitch約10um左右,預計到2029年將突破5um。3D高端封裝裏TSV Diameter W2W(Wafer to Wafer)約為1.5-2um,預計26年後最細至1um;Bond Pitch W2W約0.8-1.1um,預計26年後最細至0.5um;Wafer Thickness W2W約15-20um,預計26年後可至10um。

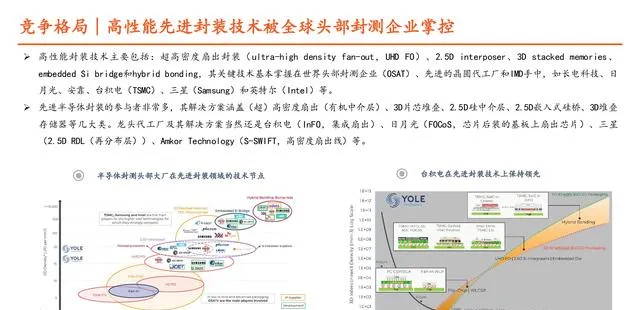

競爭格局∣高效能先進封裝技術被全球頭部封測企業掌控

高效能封裝技術主要包括:超高密度扇出封裝(ultra-high density fan-out,UHD FO)、2.5D interposer、3D stacked memories、 embedded Si bridge和hybrid bonding,其關鍵技術基本掌握在世界頭部封測企業(OSAT)、先進的晶圓代工廠和IMD手中,如長電科技、日 月光、安靠、台積電(TSMC)、三星(Samsung)和英特爾(Intel)等。先進半導體封裝的參與者非常多,其解決方案涵蓋(超)高密度扇出(有機中介層)、3D片芯堆疊、2.5D矽中介層、2.5D嵌入式矽橋、3D堆疊 記憶體等幾大類。龍頭代工廠及其解決方案當然還是台積電(InFO,整合扇出)、日月光(FOCoS,芯片後裝的基板上扇出芯片)、三星 (2.5D RDL(再分布層))、Amkor Technology(S-SWIFT,高密度扇出線)等。

國產替代∣國內半導體頭部大廠布局發力先進封裝

長電科技 XDFOI技術:公司XDFOI技術為2.5D超高密扇出型封裝,可將不同的弄能器件整合在系統封裝內,對整合度和算力有較高要求的超算領 域,如FPGA、CPU、GPU、AI和5G網路芯片等方面套用較多,將推動資訊科技的高速發展。

通富微電 VISionS技術:公司VISionS為基於超算的2.5D/3D先進封裝技術,可實作多層布線技術開發,將不同工藝不同功能的Chiplet芯片進行 高密度整合,可為客戶提供晶圓級和基板級封裝解決方案。在HBM等儲存方向布局,已完成堆疊NANDFlash和LPDDR封裝的量產,其3D儲存封裝技 術國內領先。

華天科技 3D Matrix技術:公司3D Matrix技術整合了TSV、eSiFo(Fan-out)、3D SIP等三大先進封裝技術,是Chiplet高度整合的重要技術之 一。TSV、eSiFo、3D SiP三大基礎技術,均為公司特色工藝,其中Fan-out技術為矽/基板上刻蝕挖槽,將芯片正放置凹槽內,在芯片表面與矽/ 基板表面形成扇出連線,再進行RDL布線與封裝。

長江儲存 Xtacking技術:與傳統並列式架構和CuA(CMOS under Array)架構不同,公司晶棧Xtacking 3D NAND架構可實作的金屬通道連線達 數十億根。芯片堆疊層數增加的同時,能夠帶來儲存容量的擴大,可大大提升芯片效能。

驅動端:BIS抵制&海外廠擴產倒逼國內先進封裝發展

美國制裁∣美國BIS制裁&華為榮耀陸續申請封裝專利,重要性不言而喻

美國BIS制裁劍指先進封裝:2023年10月17日,美國商務部工業和安全域(BIS)公布新的先進計算芯片、半導體制造裝置出口管制規則,意在 限制中國發展高端芯片的能力,並將於11月16日正式生效。11月21日,美國宣布了國家先進封裝制造計劃 (NAPMP)計畫,投資方向包括:材料 和載板,裝置、工具和流程,電力傳輸和熱管理,矽光通訊和連結器,Chiplet 生態系,測試、可靠性、安全性方面的Chiplet共同開發。 此舉將在後道封裝端抑制中國大陸發展高端高效能芯片,尤其是先進封裝領域。

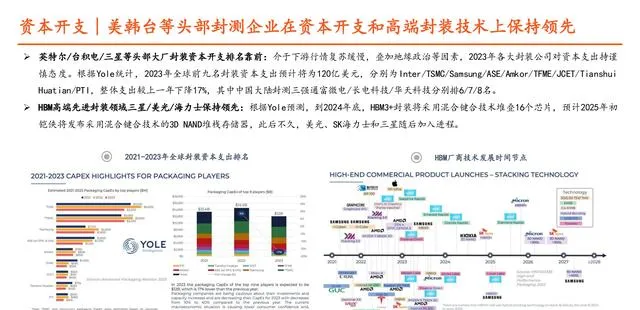

資本開支∣美韓台等頭部封測企業在資本開支和高端封裝技術上保持領先

英特爾/台積電/三星等頭部大廠封裝資本開支排名靠前:介於下遊行情復蘇緩慢,疊加地緣政治等因素,2023年各大封裝公司對資本支出持謹 慎態度。根據Yole統計,2023年全球前九名封裝資本支出預計將為120億美元,分別為Inter/TSMC/Samsung/ASE/Amkor/TFME/JCET/Tianshui Huatian/PTI,整體支出較上一年下降17%,其中中國大陸封測三強通富微電/長電科技/華天科技分別排6/7/8名。 HBM高端先進封裝領域三星/美光/海麗仕保持領先:根據Yole預測,到2024年底,HBM3+封裝將采用混合鍵合技術堆疊16個芯片,預計2025年初 鎧俠將釋出采用混合鍵合技術的3D NAND堆疊記憶體,此後不久,美光、SK海麗仕和三星隨後加入行程。

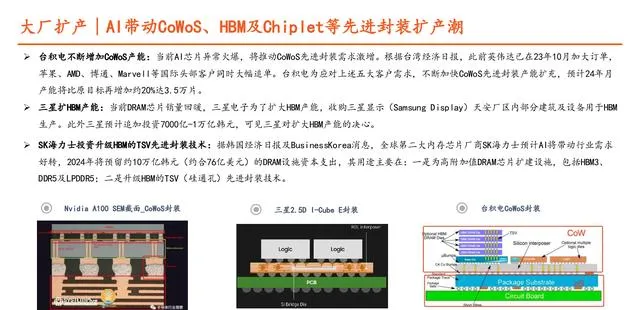

大廠擴產∣AI帶動CoWoS、HBM及Chiplet等先進封裝擴產潮

台積電不斷增加CoWoS產能:當前AI芯片異常火爆,將推動CoWoS先進封裝需求激增。根據台灣經濟日報,此前輝達已在23年10月加大訂單, 蘋果、AMD、博通、Marvell等國際頭部客戶同時大幅追單。台積電為應對上述五大客戶需求,不斷加快CoWoS先進封裝產能擴充,預計24年月 產能將比原目標再增加約20%達3.5萬片。 三星擴HBM產能:當前DRAM芯片銷量回暖,三星電子為了擴大HBM產能,收購三星顯示(Samsung Display)天安廠區內部份建築及裝置用於HBM 生產。此外三星預計追加投資7000億-1萬億韓元,可見三星對擴大HBM產能的決心。 SK海麗仕投資升級HBM的TSV先進封裝技術:據南韓經濟日報及BusinessKorea訊息,全球第二大記憶體芯片廠商SK海麗仕預計AI將帶動行業需求 好轉,2024年將預留約10萬億韓元(約合76億美元)的DRAM設施資本支出,其用途主要在:一是為高附加值DRAM芯片擴建設施,包括HBM3、 DDR5及LPDDR5;二是升級HBM的TSV(矽通孔)先進封裝技術。

TSV供應鏈∣TSV、RDL等先進封裝技術均對裝置和材料提出較高要求

先進封裝的關鍵技術TSV:TSV(Through-Silicon Via ,矽穿孔)技術透過銅、鎢、多晶矽等導電物質的填充,實作矽通孔的垂直電氣互聯。 TSV可以替代WB和FC技術,是芯片小型化的必經之路,是目前唯一的垂直電互聯技術,是實作3D先進封裝的關鍵技術之一。 制備TSV技術的裝置和材料將受益:TSV技術制備的核心關鍵步驟主要為從先把矽通孔形成(即孔刻蝕),然後沈積絕緣層或阻擋層,接著生成 銅晶種沈積,最後進行電鍍,因此制備TSV技術涉及的半導體封裝裝置和材料領域包括光刻機、塗膠顯影、刻蝕裝置、清洗裝置、鍵合裝置、 CMP等。

國產替代:產業鏈國產化率偏低,裝置&材料前景廣闊

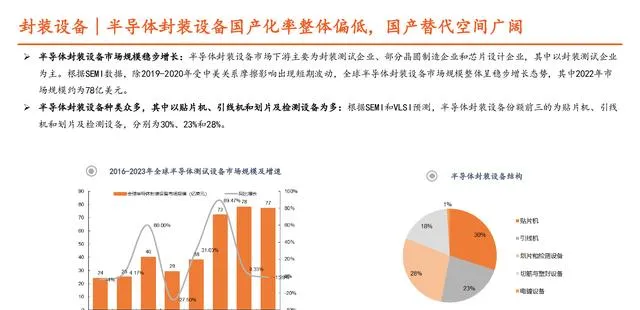

封裝裝置∣半導體封裝裝置國產化率整體偏低,國產替代空間廣闊

半導體封裝裝置市場規模穩步增長:半導體封裝裝置市場下遊主要為封裝測試企業、部份晶圓制造企業和芯片設計企業,其中以封裝測試企業 為主。根據SEMI數據,除2019-2020年受中美關系摩擦影響出現短期波動,全球半導體封裝裝置市場規模整體呈穩步增長態勢,其中2022年市 場規模約為78億美元。

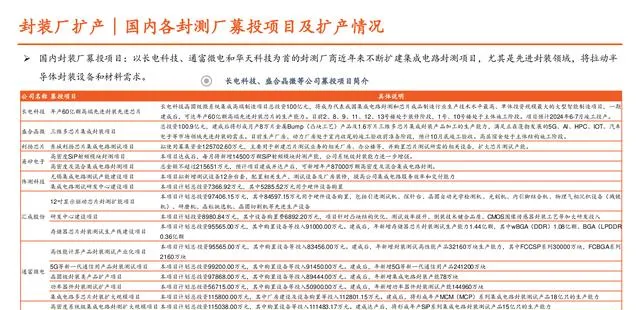

封裝裝置∣國內先進封裝裝置鏈全面發展

封裝裝置分別有固晶機、鍵合機、曝光機、點膠機、劃片機、測試機、分選機、探針台等,國際廠商如DISCO在劃片機、減薄機等領域占據大 部份份額,K&S在貼片機、鍵合機等領域占據主導地位。隨著國內封測代工三強進入全球前十,推動國內半導體封裝裝置的發展,如光力科技, 在劃片機領域處於國內龍頭地位。隨著先進封裝占比逐漸走高,國內半導體封裝裝置將不斷受益。

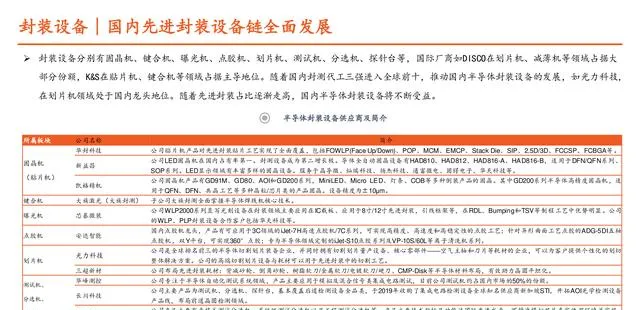

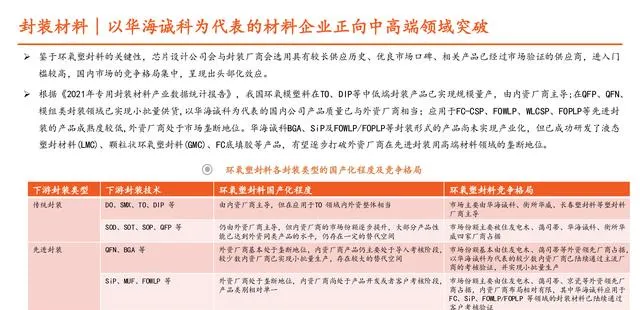

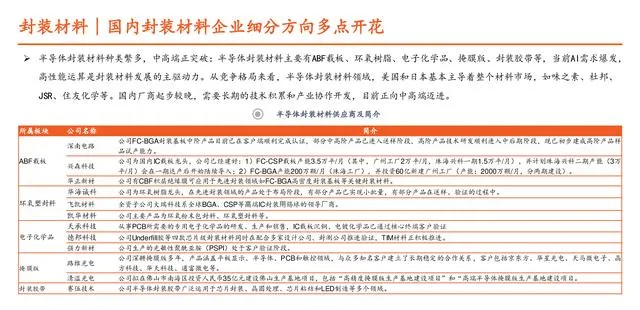

封裝材料∣國內封裝材料企業細分方向多點開花

半導體封裝材料種類繁多,中高端正突破:半導體封裝材料主要有ABF載板、環氧樹脂、電子化學品、掩膜版、封裝膠帶等,當前AI需求爆發, 高效能運算是封裝材料發展的主驅動力。從競爭格局來看,半導體封裝材料領域,美國和日本基本主導著整個材料市場,如味之素、杜邦、 JSR、住友化學等。國內廠商起步較晚,需要長期的技術積累和產業協作開發,目前正向中高端邁進。

報告節選:

(本文僅供參考,不代表我們的任何投資建議。如需使用相關資訊,請參閱報告原文。)

精選報告來源:【未來智庫】。「連結」